VIVADO软件DDS信号发生器Verilog语言的任意波形发生器

名称:VIVADO软件DDS信号发生器Verilog语言的任意波形发生器(代码在文末下载)

软件:VIVADO

语言:Verilog

代码功能:

1.可产生正弦波,锯齿波,三角波,方波4种波形

2.输出波形的频率可调、相位可调、幅值可调

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

演示视频:

设计文档:

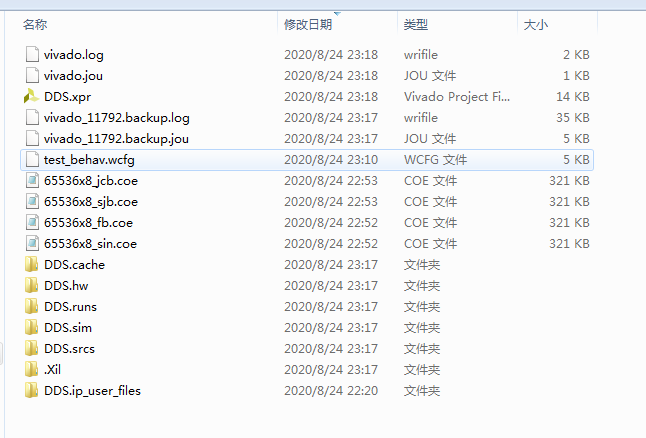

1. 工程文件

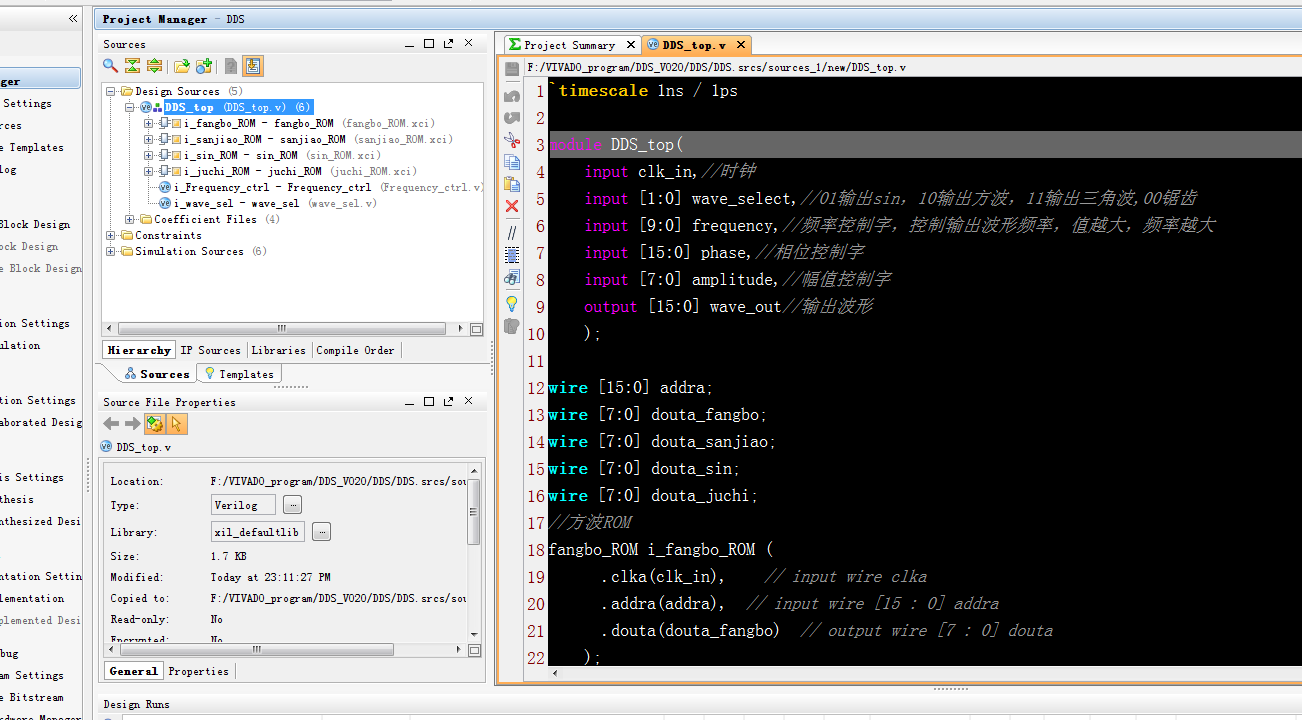

2. 程序文件

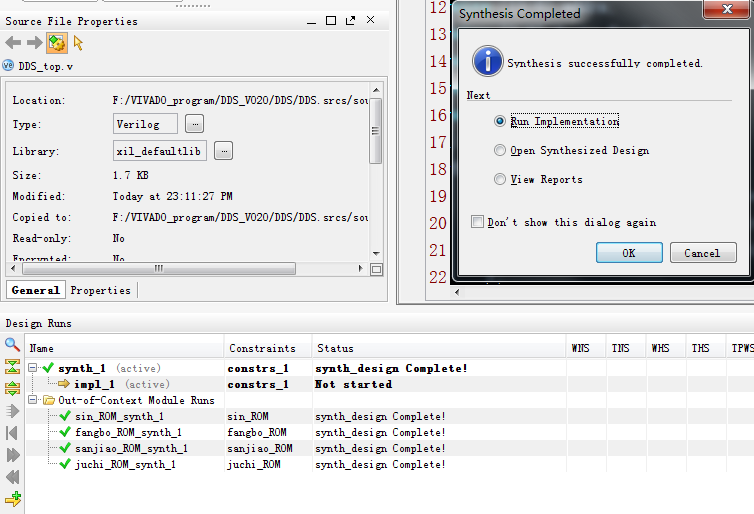

3. 程序编译

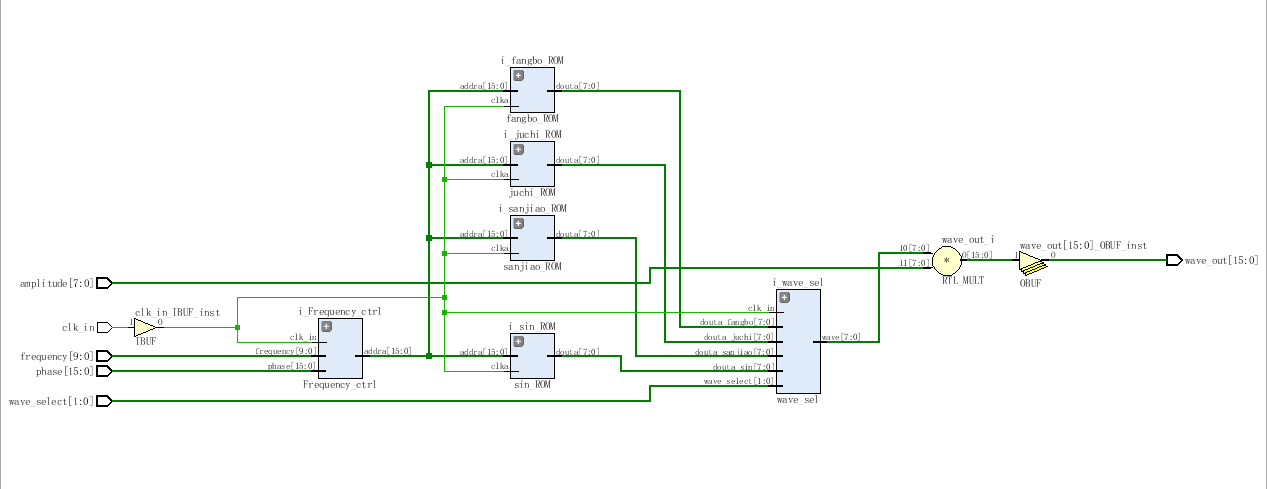

4. RTL图

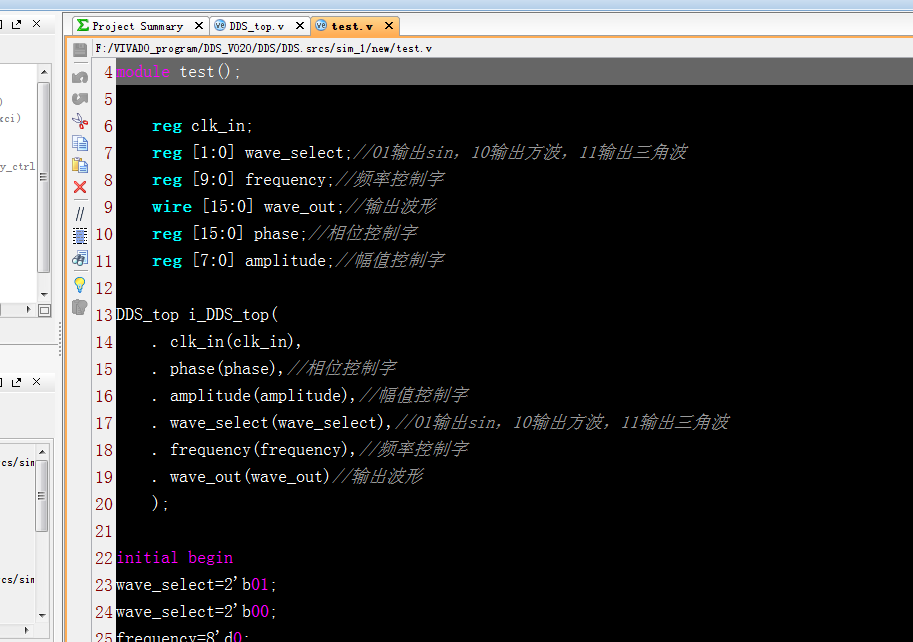

5. Testbench

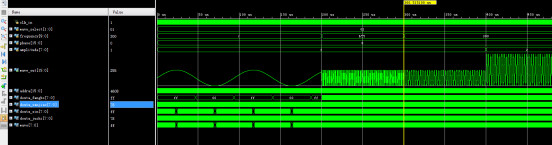

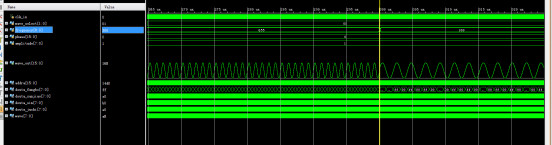

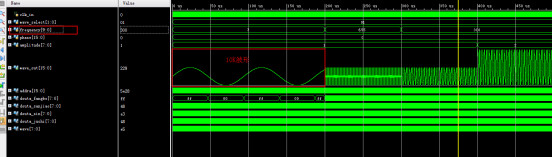

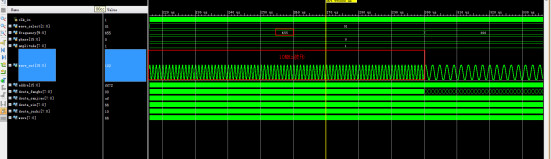

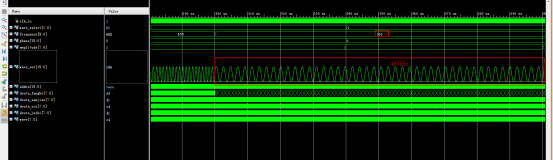

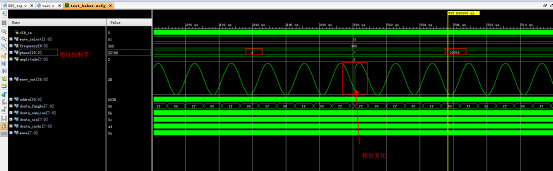

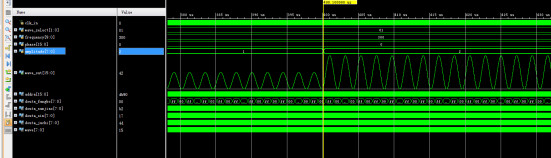

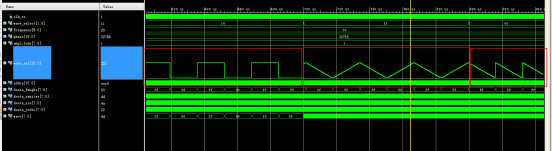

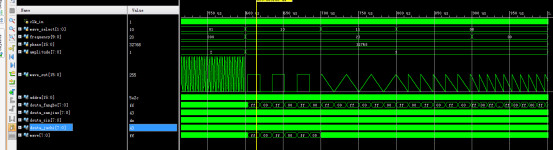

6. 仿真图

1. 任意正弦波输出

2. 10K、1MHz、10K~1MHz波形

3. 对应频率控制字和相位控制字

![]()

4. 不同初相正弦波

5. 不同振幅、均值正弦波

6. 方波、锯齿波、三角波等

部分代码展示:

`timescale 1ns / 1ps module DDS_top( input clk_in,//时钟 input [1:0] wave_select,//01输出sin,10输出方波,11输出三角波,00锯齿 input [9:0] frequency,//频率控制字,控制输出波形频率,值越大,频率越大 input [15:0] phase,//相位控制字 input [7:0] amplitude,//幅值控制字 output [15:0] wave_out//输出波形 ); wire [15:0] addra; wire [7:0] douta_fangbo; wire [7:0] douta_sanjiao; wire [7:0] douta_sin; wire [7:0] douta_juchi; //方波ROM fangbo_ROM i_fangbo_ROM ( .clka(clk_in), // input wire clka .addra(addra), // input wire [15 : 0] addra .douta(douta_fangbo) // output wire [7 : 0] douta ); //三角波ROM sanjiao_ROM i_sanjiao_ROM ( .clka(clk_in), // input wire clka .addra(addra), // input wire [15 : 0] addra .douta(douta_sanjiao) // output wire [7 : 0] douta ); //sin波ROM sin_ROM i_sin_ROM ( .clka(clk_in), // input wire clka .addra(addra), // input wire [15 : 0] addra .douta(douta_sin) // output wire [7 : 0] douta ); //锯齿 juchi_ROM i_juchi_ROM ( .clka(clk_in), // input wire clka .addra(addra), // input wire [15 : 0] addra .douta(douta_juchi) // output wire [7 : 0] douta ); //相位累加器 Frequency_ctrl i_Frequency_ctrl( . clk_in(clk_in), . frequency(frequency),//频率控制字 . phase(phase),//相位控制字 . addra(addra)//输出地址 ); wire [7:0] wave; //波形选择控制 wave_sel i_wave_sel( . clk_in(clk_in), . wave_select(wave_select),//01输出sin,10输出方波,11输出三角波 . douta_fangbo(douta_fangbo),//方波 . douta_sanjiao(douta_sanjiao),//三角 . douta_juchi(douta_juchi),//锯齿 . douta_sin(douta_sin), //正弦 . wave(wave)//输出波形 ); assign wave_out=wave*amplitude;//输出波形 endmodule

代码文件(付费下载):

![]()

1、代码文件需要付费后才可见。

2、支付问题请联系微信公众号客服。

3、优质Verilog/VHDL代码资源,所见即所得。

Verilog/VHDL资源下载 » VIVADO软件DDS信号发生器Verilog语言的任意波形发生器

2、支付问题请联系微信公众号客服。

3、优质Verilog/VHDL代码资源,所见即所得。

Verilog/VHDL资源下载 » VIVADO软件DDS信号发生器Verilog语言的任意波形发生器

发表评论