QuartusFIR低通滤波器设计verilog代码仿真

名称:QuartusFIR低通滤波器设计verilog代码仿真

软件:Quartus

语言:Verilog

代码功能:

FIR低通滤波器设计

使用移位、相乘再相加的的方式设计FIR低通滤波器

滤波器系数如下:

Radix = 16;

Coefficient_Width = 12;

CoefData = 1be,

2d8,

3de,

498,

4db,

498,

3de,

2d8,

1be;

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

演示视频:

设计文档:

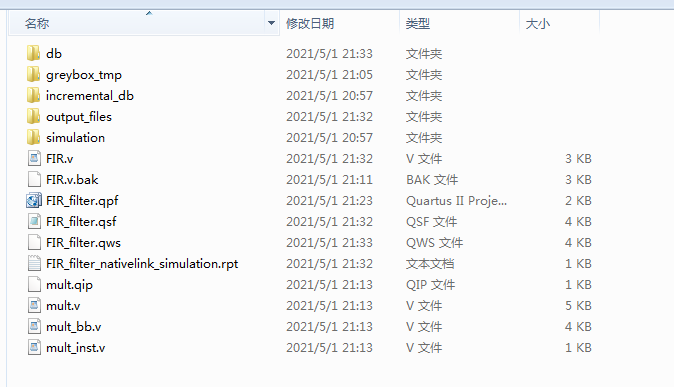

1. 工程文件

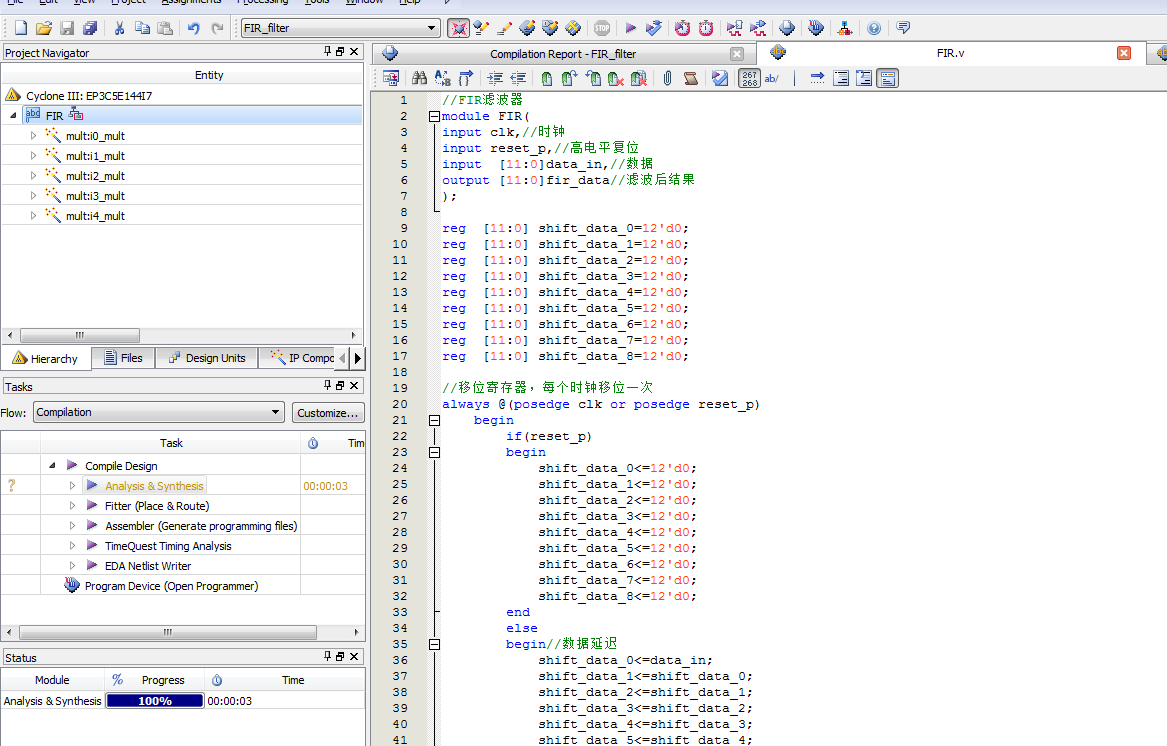

2. 程序文件

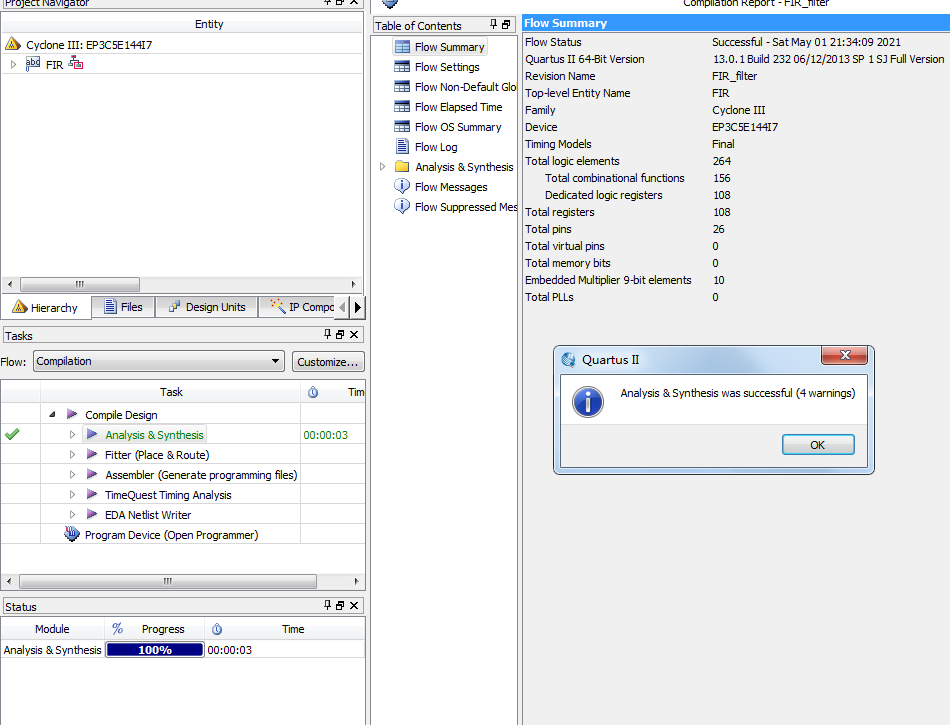

3. 程序编译

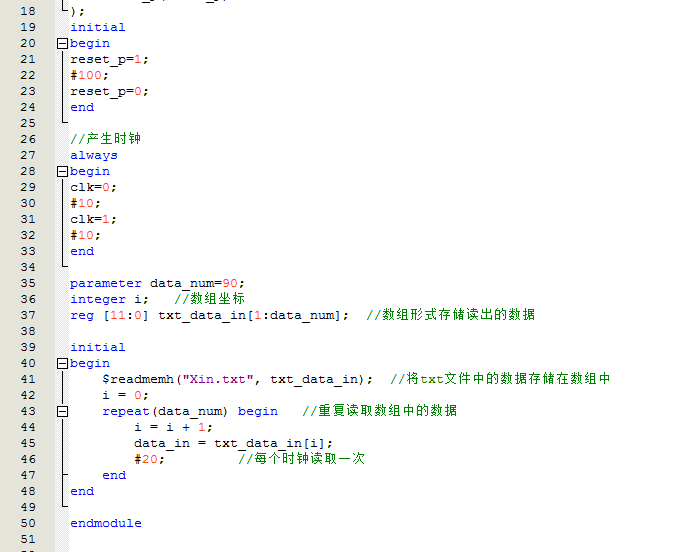

4. Testebnch

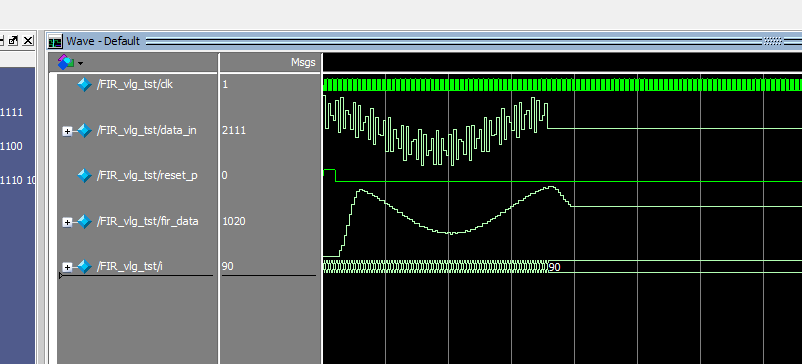

5. 仿真图

部分代码展示:

//FIR滤波器 module FIR( input clk,//时钟 input reset_p,//高电平复位 input [11:0]data_in,//数据 output [11:0]fir_data//滤波后结果 ); reg [11:0] shift_data_0=12'd0; reg [11:0] shift_data_1=12'd0; reg [11:0] shift_data_2=12'd0; reg [11:0] shift_data_3=12'd0; reg [11:0] shift_data_4=12'd0; reg [11:0] shift_data_5=12'd0; reg [11:0] shift_data_6=12'd0; reg [11:0] shift_data_7=12'd0; reg [11:0] shift_data_8=12'd0; //移位寄存器,每个时钟移位一次 always @(posedge clk or posedge reset_p) begin if(reset_p) begin shift_data_0<=12'd0; shift_data_1<=12'd0; shift_data_2<=12'd0; shift_data_3<=12'd0; shift_data_4<=12'd0; shift_data_5<=12'd0; shift_data_6<=12'd0; shift_data_7<=12'd0; shift_data_8<=12'd0; end else begin//数据延迟 shift_data_0<=data_in; shift_data_1<=shift_data_0; shift_data_2<=shift_data_1; shift_data_3<=shift_data_2; shift_data_4<=shift_data_3; shift_data_5<=shift_data_4; shift_data_6<=shift_data_5; shift_data_7<=shift_data_6; shift_data_8<=shift_data_7; end end wire [12:0] add_0; wire [12:0] add_1; wire [12:0] add_2; wire [12:0] add_3; wire [12:0] add_4; assign add_0=shift_data_0+shift_data_8; assign add_1=shift_data_1+shift_data_7; assign add_2=shift_data_2+shift_data_6; assign add_3=shift_data_3+shift_data_5; assign add_4=shift_data_4; wire [24:0] mul_data_0; wire [24:0] mul_data_1; wire [24:0] mul_data_2; wire [24:0] mul_data_3; wire [24:0] mul_data_4; //1be, //2d8, //3de, //498, //4db, //498, //3de, //2d8, //1be; //input clock; //input[12:0] dataa; //input[11:0] datab; //output[24:0] result; //调用乘法器IP multi0_mult ( .clock ( clk ), .dataa ( add_0 ), .datab ( 12'h1be ), .result ( mul_data_0 ) ); multi1_mult ( .clock ( clk ), .dataa ( add_1 ), .datab ( 12'h2d8 ), .result ( mul_data_1 ) ); multi2_mult ( .clock ( clk ), .dataa ( add_2 ), .datab ( 12'h3de ), .result ( mul_data_2 ) ); multi3_mult ( .clock ( clk ), .dataa ( add_3 ), .datab ( 12'h498 ), .result ( mul_data_3 ) ); multi4_mult ( .clock ( clk ), .dataa ( add_4 ), .datab ( 12'h4db ), .result ( mul_data_4 ) ); wire [25:0] fir_add; assign fir_add=mul_data_0+mul_data_1+mul_data_2+mul_data_3+mul_data_4; assign fir_data=fir_add[25:14];//取高12位输出 endmodule

代码文件(付费下载):

![]()

1、代码文件需要付费后才可见。

2、支付问题请联系微信公众号客服。

3、优质Verilog/VHDL代码资源,所见即所得。

Verilog/VHDL资源下载 » QuartusFIR低通滤波器设计verilog代码仿真

2、支付问题请联系微信公众号客服。

3、优质Verilog/VHDL代码资源,所见即所得。

Verilog/VHDL资源下载 » QuartusFIR低通滤波器设计verilog代码仿真

发表评论