SPWM波发生器VHDL语言正弦波脉宽调制quartus仿真

名称:SPWM波发生器VHDL语言正弦波脉宽调制(代码在文末下载)

软件:Quartus II

语言:VHDL

代码功能:

完成基于FPGA的SPWM发生器的设计,输出1路SPWM信号。

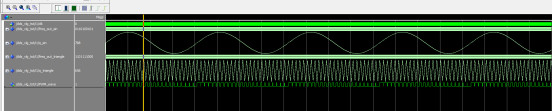

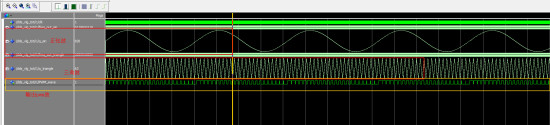

实现的方法:分别产生正弦波和三角波,将正弦波和三角波进行比较,三角波大于正弦波时输出1,否则输出0

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

演示视频:

设计文档:

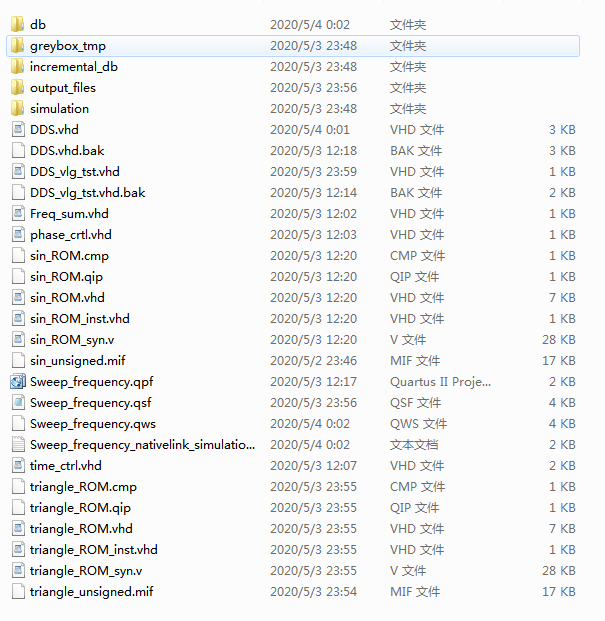

1. 工程文件

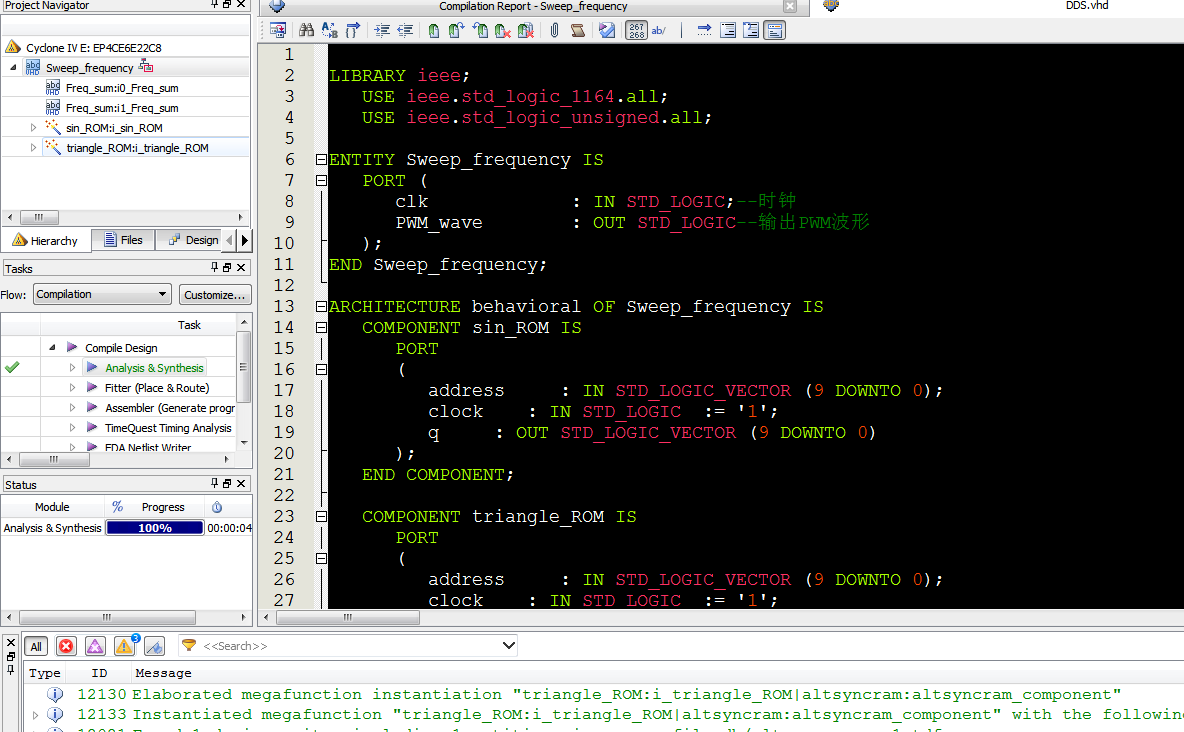

2. 程序文件

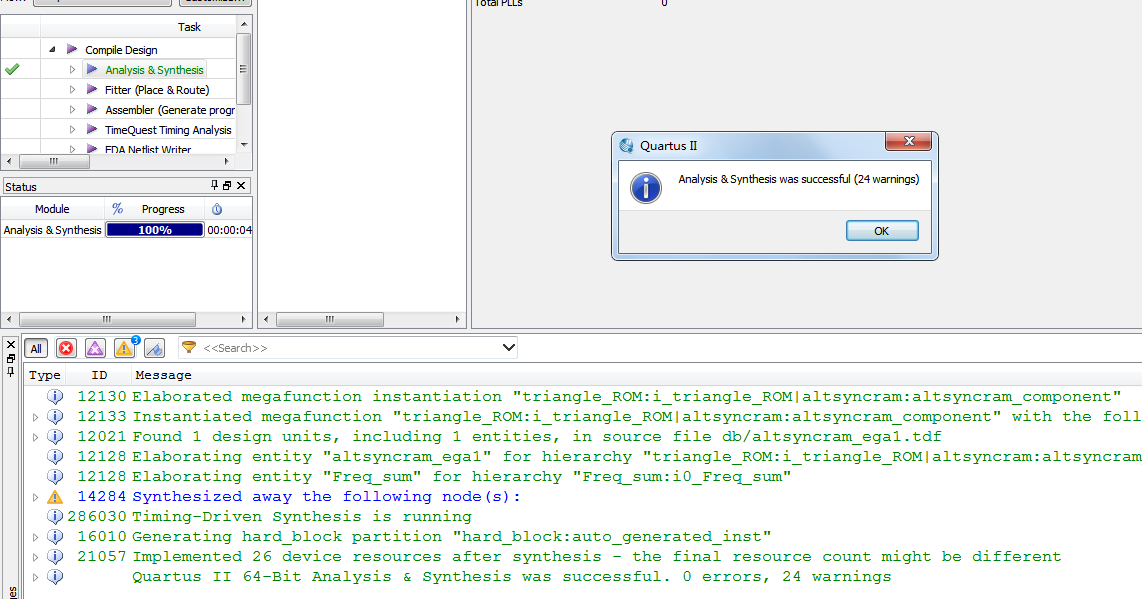

3. 程序编译

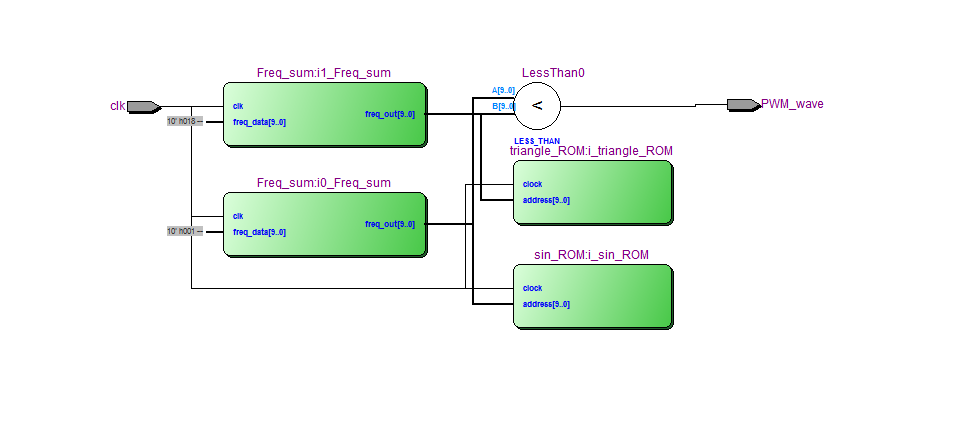

4. RTL图

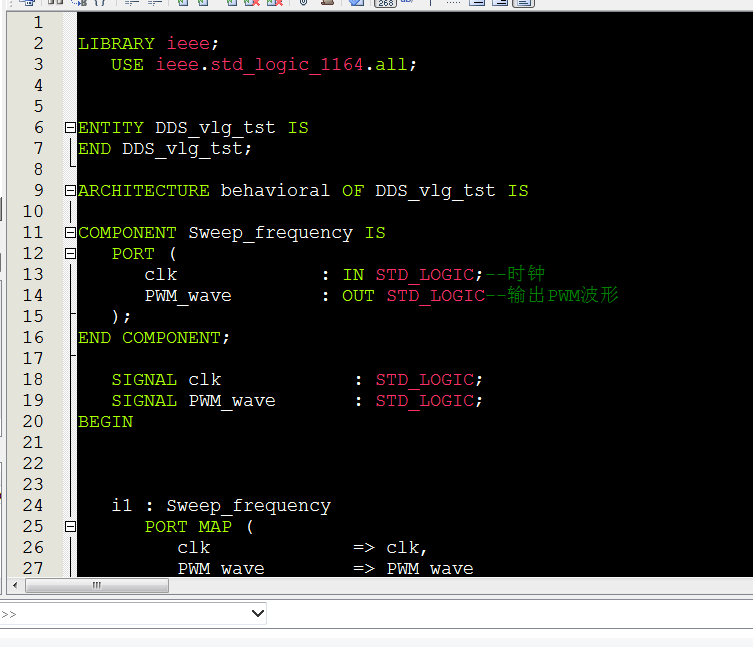

5. Testbench

6. 仿真图

相位累加器模块

三角波ROM模块

正弦波ROM模块

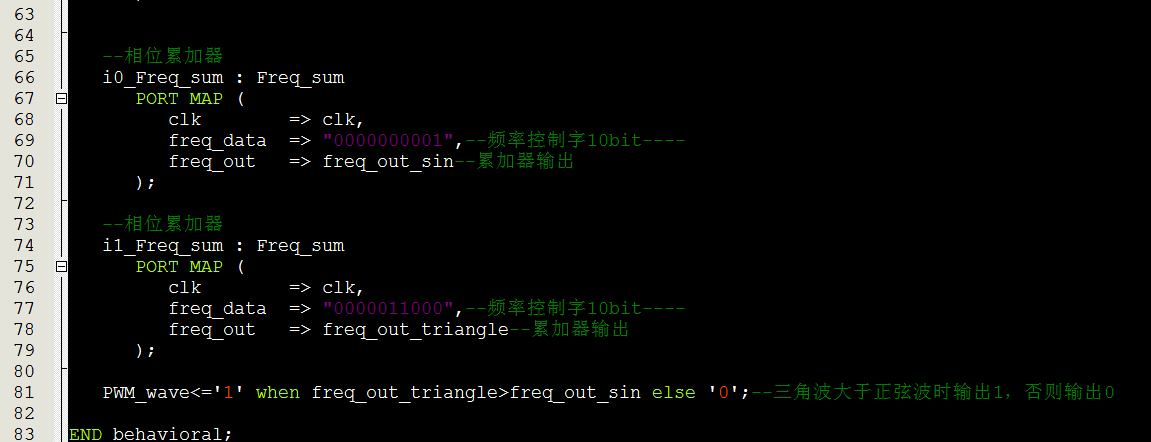

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ENTITY Sweep_frequency IS PORT ( clk : IN STD_LOGIC;--时钟 PWM_wave : OUT STD_LOGIC--输出PWM波形 ); END Sweep_frequency; ARCHITECTURE behavioral OF Sweep_frequency IS COMPONENT sin_ROM IS PORT ( address: IN STD_LOGIC_VECTOR (9 DOWNTO 0); clock: IN STD_LOGIC := '1'; q: OUT STD_LOGIC_VECTOR (9 DOWNTO 0) ); END COMPONENT; COMPONENT triangle_ROM IS PORT ( address: IN STD_LOGIC_VECTOR (9 DOWNTO 0); clock: IN STD_LOGIC := '1'; q: OUT STD_LOGIC_VECTOR (9 DOWNTO 0) ); END COMPONENT; COMPONENT Freq_sum IS PORT ( clk : IN STD_LOGIC; freq_data : IN STD_LOGIC_VECTOR(9 DOWNTO 0); freq_out : OUT STD_LOGIC_VECTOR(9 DOWNTO 0) ); END COMPONENT; SIGNAL freq_out_sin : STD_LOGIC_VECTOR(9 DOWNTO 0); SIGNAL q_sin : STD_LOGIC_VECTOR(9 DOWNTO 0);--ROM输出波形 SIGNAL freq_out_triangle : STD_LOGIC_VECTOR(9 DOWNTO 0); SIGNAL q_triangle : STD_LOGIC_VECTOR(9 DOWNTO 0);--ROM输出波形 BEGIN --sin存储Rom表 i_sin_ROM : sin_ROM PORT MAP ( address => freq_out_sin,--查找表地址 clock => clk,--时钟 q => q_sin--输出波形 ); --triangle存储Rom表 i_triangle_ROM : triangle_ROM PORT MAP ( address => freq_out_triangle,--查找表地址 clock => clk,--时钟 q => q_triangle--输出波形 ); --相位累加器 i0_Freq_sum : Freq_sum PORT MAP ( clk => clk, freq_data => "0000000001",--频率控制字10bit---- freq_out => freq_out_sin--累加器输出 ); --相位累加器 i1_Freq_sum : Freq_sum PORT MAP ( clk => clk, freq_data => "0000011000",--频率控制字10bit---- freq_out => freq_out_triangle--累加器输出 ); PWM_wave<='1' when freq_out_triangle>freq_out_sin else '0';--三角波大于正弦波时输出1,否则输出0 END behavioral;

代码文件(付费下载):

![]()

1、代码文件需要付费后才可见。

2、支付问题请联系微信公众号客服。

3、优质Verilog/VHDL代码资源,所见即所得。

Verilog/VHDL资源下载 » SPWM波发生器VHDL语言正弦波脉宽调制quartus仿真

2、支付问题请联系微信公众号客服。

3、优质Verilog/VHDL代码资源,所见即所得。

Verilog/VHDL资源下载 » SPWM波发生器VHDL语言正弦波脉宽调制quartus仿真

发表评论